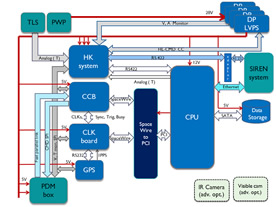

Data Handling Subsystem

The Italian collaboration is in charge for the hardware and software of the data handling subsystem and GPS.

The Data Handling subsystem controls the front-end electronics, performs the 2nd level trigger filtering, tags events with arrival time (UTC) and payload position (GPS), manages the Mass Memory for data storage, measures operating and dead time of the instrument, provides signals for time synchronization of the event, performs housekeeping monitor, handles interface to telecommands and to telemetry system.

The DP functionalities are obtained by connecting different specialized items, which form a complex system. The main sub-assembly items are:

- Control Cluster Board (CCB)

- CPU

- Data storage (DST)

- Housekeeping system (HK)

- Clock Board (CLKB)

- GPS receiver (GPSR)

- Data Processor Power Supply (DP-LVPS)

The CCB has a direct connection to the PDM through a 40 MHz parallel bus. It processes and classifies the received data performing the 2nd level trigger.

The CPU receives science data from the CCB and from the Clock board. For each trigger roughly 330 kB of data are transmitted via SpaceWire protocol from CCB to the CPU. The CPU Motherboard is the iTX-i2705 model, manufactured by Arbor.

The mass storage is composed by an array of two Solid State Drive (SSD, 1TB each) operating in disks fault-tolerant mode RAID-1, connected by two SATA ports.

The clock and time synchronization board is the part of the data processor that ensure the time synchronization of the events. The board has an interface with a GPS receiver which allows to collect, for each event, information on the position of the instrument and the UTC time with a precision of few microseconds. The CLK board receives the 2nd level trigger signal from the CCB and a release-busy signal from CPU. These two signals drive the logic implemented on the board to measure the live time and dead time of the apparatus. The CLKB receives commands from CPU and transmits data to the CPU by using the SpaceWire communication protocol. An FPGA Xilinx Virtex5 implements all the required functionalities of the CLKB.

The House-Keeping system collects telemetry from several sub-systems of the instrument in slow control mode. It is responsible for monitoring voltages and currents of the Low Voltage Power Supply, has a serial bus to convey telemetry and tele-commands through the CPU interface and to other sub-systems. The HK is implemented around an off-the-shelf microcontroller board (Arduino Mega 2560), combined with 5 custom-made protocol interface boards to pre-process the various signals.

The DP mass and power budgets are 15 Kg and 50 W respectively.

The CPU and its external connections are reported in Figure.

The subsystem is managed by a modular and multitasking software.