Data Acquisition Subsystem

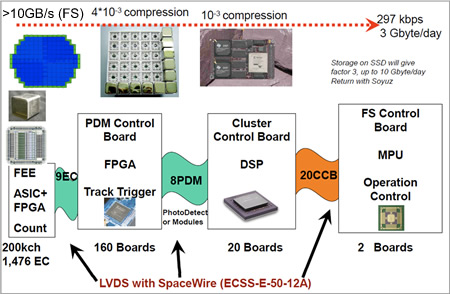

An ASIC chip performs photo-electron signal readout and conversion for the 64 channels of the MAPMT. An FPGA handles first level trigger data on a PDM level (reading 36 MAPMTs). The data are stored in a 128 GTU buffer (each GTU corresponds to a 2.5 μs frame, for a total sampling of 320 μs) upon which the triggering and noise reduction algorithms are implemented. Background events are rejected by a factor 103.Second level triggering algorithms are implemented by the 18 CCB (Cluster Control Boards), DSPs with about 1Gflop computing capability which further process triggers coming from 8 PDMs. At this level background is rejected by another factor 103. A housekeeping electronic system and low and high voltage power supplies complete the electronic chain.

The data are managed by a Storage and Control Unit System composed of a CPU mainboard and a Mass Memory. Data stored in the Mass Memory are periodically sent to ISS via a high speed link based on Ethernet protocol. Data are subsequently downlinked to the ground via TDRSS satellite link or stored on hard disks.